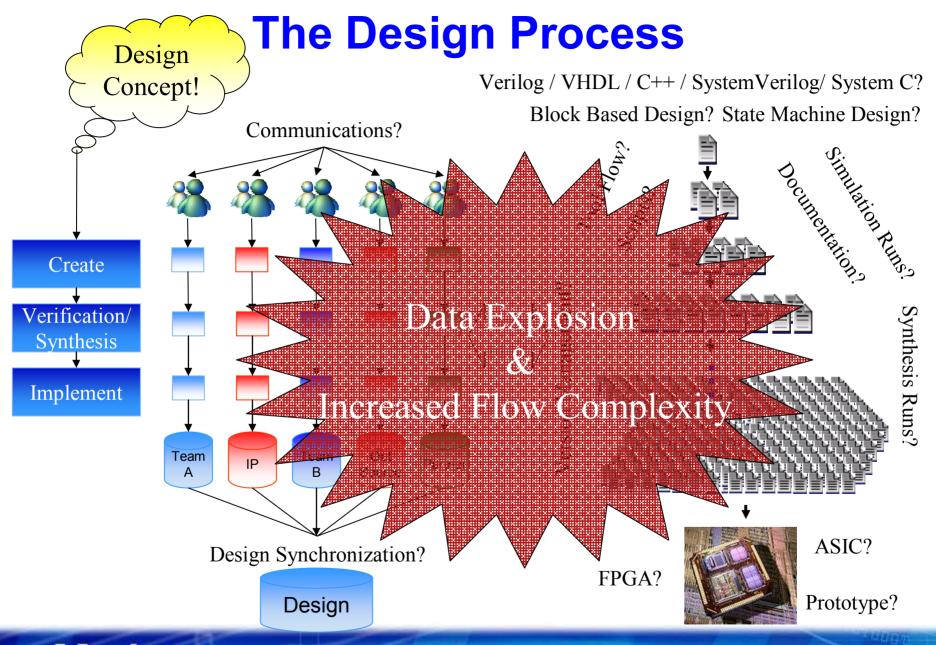

### Can your processes be improved?

Processes Effect

**Productivity**

Quality

Risk

Team Design

**Partitioning**

Unify Different Environments

Staff Portability

**Environment**

Capture/Checking

**HVLs & HDLs**

Complexity

**Understanding**

Existing & Legacy

Design Re-Use

IP

#### **HDL Designer Improves Your Engineering Process & Data Management**

Data Management

Versioning

Maintenance

**Archiving**

**Flows**

**New Methodologies**

Consistency & Repeatability

Simulation & Synthesis

Verification

Debugging

Regression

Closure/Sign-Off

**Documentation**

**Reviews**

Quality

Customer

#### **Quotes & statements to consider**

Major European Chip Manufacture - ASIC Design Manager

"How do you manually interact with 1M lines of code and 10,000 related design files? Tools like HDS are critical in our design flow to access and manage design data"

"...We have worked with Mentor to customize HDS to implement our Core ReUse Methodology."

Over a third of all high-end ASIC designers now use FPGAs for prototyping 500,000-plus-gate designs.

"...Design managers report that at least 50% of their engineering resource is devoted to managing the push of design data through the tools in their flows." -1/4/05

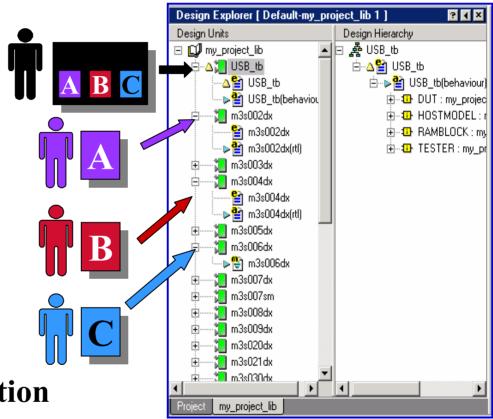

### **Team Design**

- Better use of Libraries

- Bottom-Up & Top-DownDesign Styles

- Text and/or Graphics

- Environment & Flows Common

Quality Design Documentation

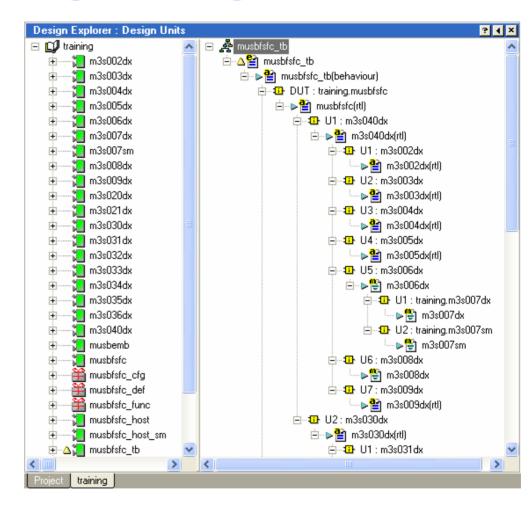

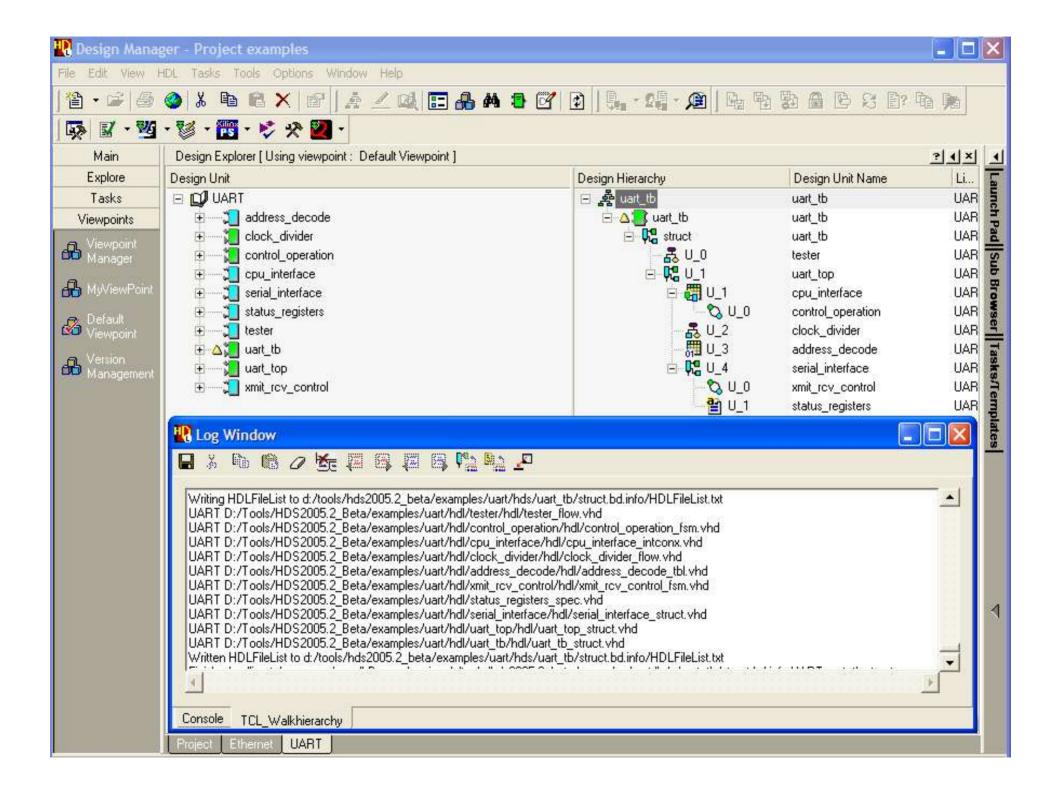

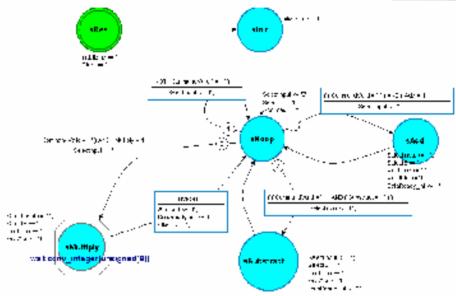

# **Understand & Manage Design Database**

- **■** Import/reference mechanisms

- HDL code parser

- Hierarchy understood

- Unit/Hierarchy View

- Cross Referencing/Highlight

- Searches Find/Where used

- VHDL Configurations

- Easy design navigation

- Pure Text and/or Graphics

- Rendering of Text2Graphics

- Engineering Logbook

- Store relevant Documents/Scripts/Programs within Environment

# **Version Management**

Check In, Check Out, Get, Change Lock, Label, Synchronize, Status, History, Compare

- Need to keep track of changes

- Back track and/or modify existing design

- Simple interface

- **Easy to use and low impact**

- 3<sup>rd</sup>-party version management:

- -GNU RCS or CVS

- -Microsoft Visual Source Safe<sup>™</sup> (VSS)

- Rational (IBM) ClearCase<sup>TM</sup>

- Synchronicity DesignSync<sup>™</sup>

- ClioSoft SOSTM

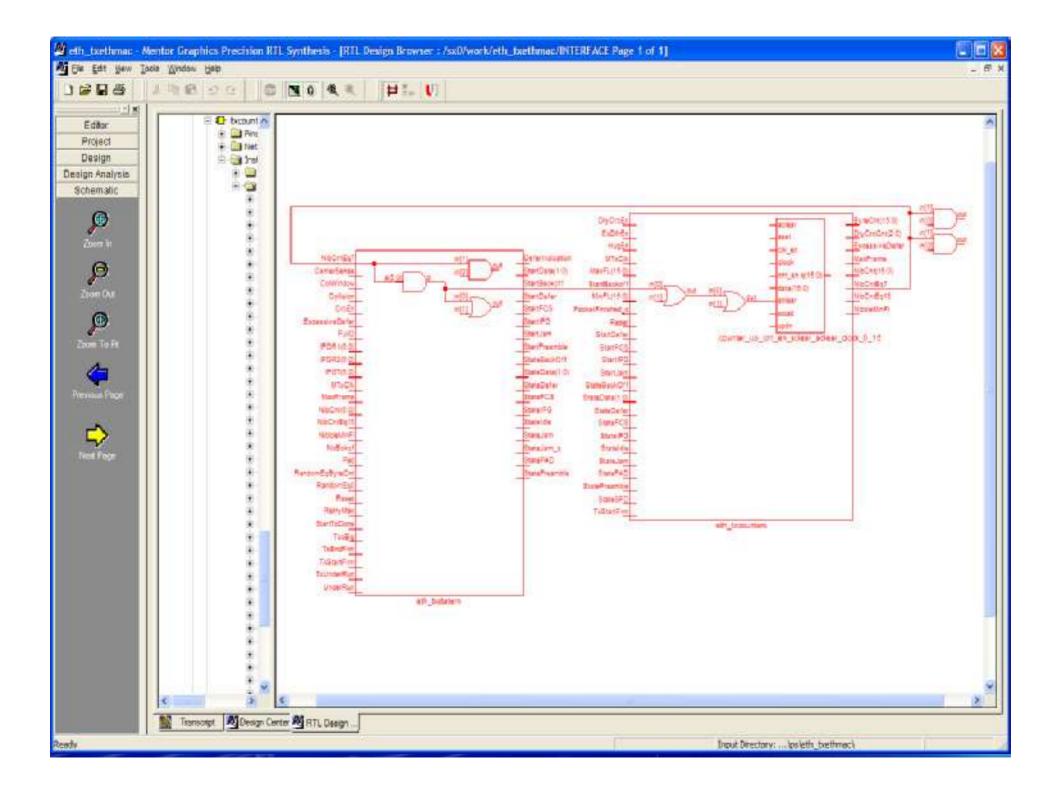

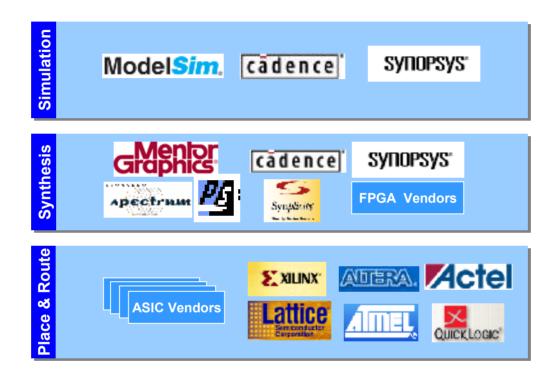

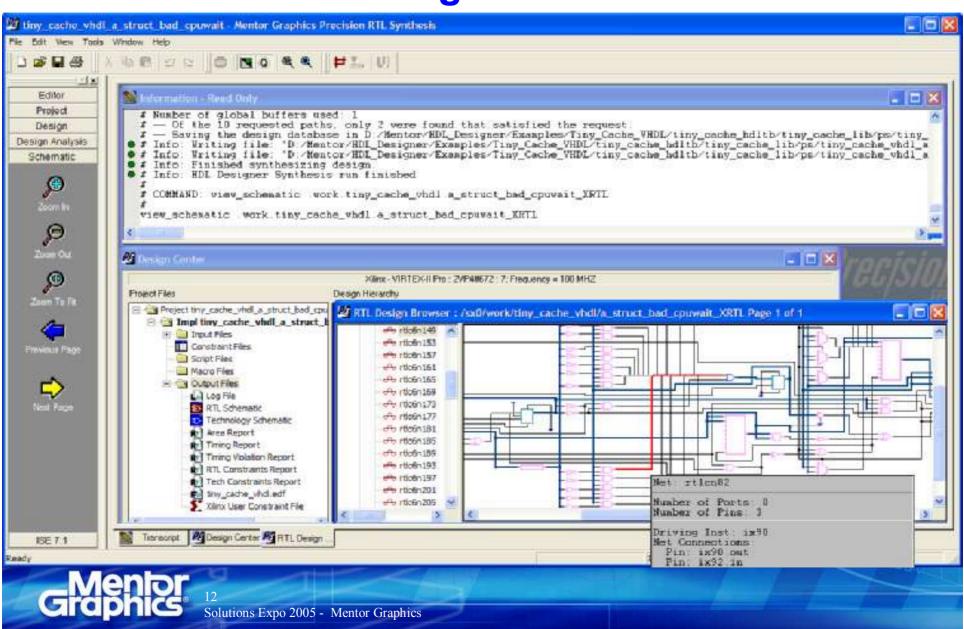

### **Downstream Tool/Flow Integration**

Focus on system rather than process issues!

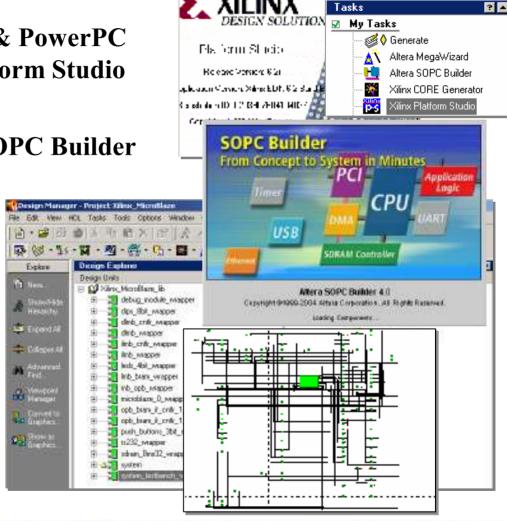

# Xilinx & Altera CPU Integration

Supports Xilinx MicroBlaze & PowerPC CPU's with Xilinx EDK Platform Studio

Supports Altera CPU with SOPC Builder

- ModelSim simulation view in HDL Designer browser

- Synthesis view for Precision Synthesis & LeonardoSpectrum in Side Data

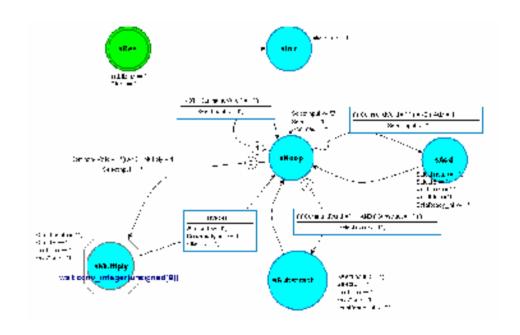

### **Automated Design Documentation**

- Make design communications easier for all

- Design Comprehension

- Design review

- Multi-site design sharing

- Lifecycle maintenance

- HDL Designer helps

- Renders graphics

- Block diagrams

- State machine charts

- Dynamic HTML Export

# HDL Designer provides a complete Design, Data & Process Management Environment

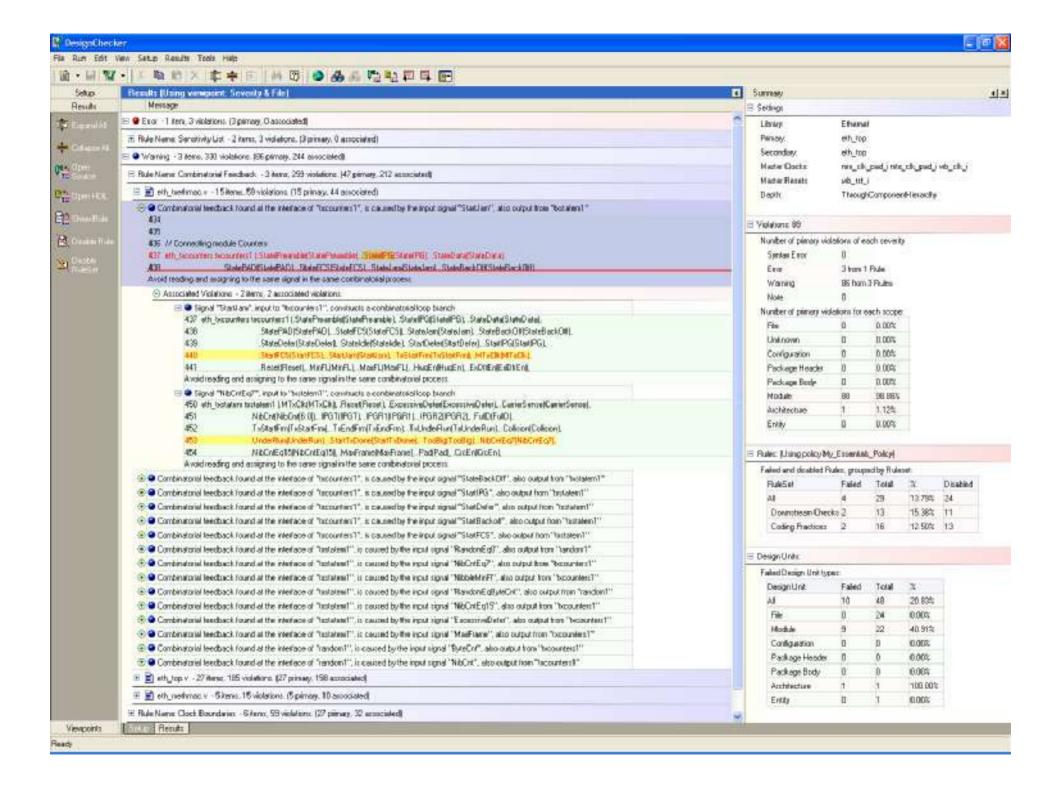

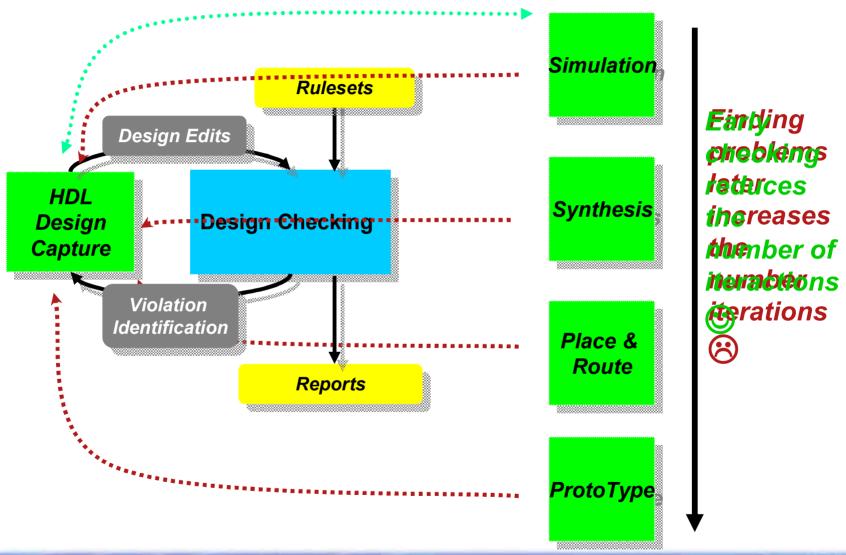

### **HDL Designer - DesignChecker**

- Check for issues as the code is written!

- Identifies coding/design bugs earlier

- Checking at the end of a project is too late!

- Result Better Quality code at the time of creation

### Where Does Static Design Checker Fit?

# **Detect with Static Design Checking**

#### **Checks that:**

- Validates Code Standalone or Hierarchically

- NO translation to a gate-level netlist

- NO synthesis, simulation, DFT, or formal engines

### What Types of Checks can be Performed?

- Allow

- Assignments

- Clocks & Resets

- Conditions

- Configurations

- Declarations

- Directives

- Format

- FSM

- Gates

- HDL Syntax & Semantics

- Instances

- Labels

- Naming

- Order

- Partitioning

- Pragmas

- Race Conditions

- Ranges

- Registers

- Sensitivity

- Subprograms

- VITAL

### **Built-In Rulesets**

Supports out-of-the-box use

**Built using base rules**

- Reuse Methodology Manual- 3<sup>rd</sup> Edition

- Essentials default, core checks

- Altera

- Xilinx

- Quality IP scoring matrix VSI Alliance (soon)

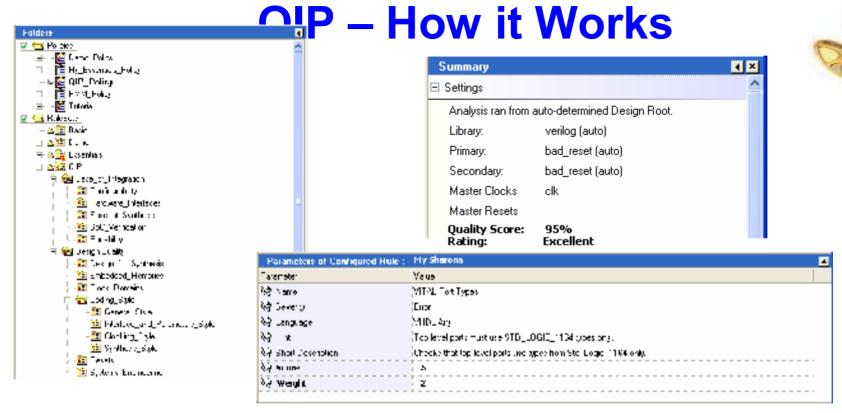

# **QIP Support**

- Quality IP scoring matrix from VSI Alliance

- Manually fill out the dynamic spreadsheet & get a score

- If the score is low, add significant time to your Time<sub>Reuse</sub> variable

www.vsi.org

| QIP-v11 06-xik                                                            |                                                | <u> </u> |  |

|---------------------------------------------------------------------------|------------------------------------------------|----------|--|

| A.                                                                        |                                                | -0       |  |

| VirtualComponentName                                                      | Scoring Summaries                              |          |  |

| VCVendorCompany                                                           | IP Ease of Rouse                               | 0%       |  |

| areas dosestratores as established                                        | Design & Verification Quality                  | 0%       |  |

|                                                                           | IP Maturity                                    | 0%       |  |

| Copyright © 2003 VSIA                                                     | Vendor Assessment                              |          |  |

| Cummany Banast                                                            | Total                                          |          |  |

| Summary Report                                                            | Design Guality                                 | 0%       |  |

| Jena Release                                                              | Verification Quality                           | 9%       |  |

| Technical Support                                                         | Answers that are unacceptable                  |          |  |

| Answ                                                                      | e <u>rs that are acceptable but add risk</u> t |          |  |

|                                                                           | Answers that are acceptable                    |          |  |

|                                                                           | Total                                          | 0        |  |

| PNAME                                                                     | VirtualComponentName                           |          |  |

| SupplierName                                                              | VCVendarCompany                                |          |  |

| Select the type of block you are evaluating                               | mixed-signal IP                                |          |  |

| tre you the IP developer or the end-user                                  | Spreadsheet reviewer                           |          |  |

| Are you interested in a traffic light report                              | Yes                                            |          |  |

|                                                                           | Score                                          | - 16     |  |

| P Maturity Assessment                                                     | 0                                              | 0%       |  |

| Vendor Assessment                                                         | 0                                              | 0%       |  |

| P Ease of Reuse (IP Integrator's View)                                    | 0                                              | 8%       |  |

| Documentation Quality                                                     | 0                                              | 0%       |  |

| Digital Soft IP: Documentation Quality                                    | 0                                              | 0%       |  |

| Digital Verification IP: Documentation Quality                            | D                                              | 0%       |  |

| Embedded Software: Documentation Quality                                  | 0                                              | 0%       |  |

| Analog IP: Documentation Quality                                          | D                                              | 0%       |  |

| Ease of Integration                                                       | 0                                              | 0%       |  |

| Digital Soft IP: Ressability                                              | 0                                              | 0%       |  |

| Digital Verification IP: Reusability                                      | D                                              | 0%       |  |

| Embedded Software: Reusability                                            | 0                                              | 0%       |  |

| Analog IP: Remability                                                     | 0                                              | 0%       |  |

| Design & Verification Quality (IP Developers' View):                      | . 0                                            | 8%       |  |

| Dosign Guality                                                            | D D                                            | 0%       |  |

| Digital Soft IP: Design Quality                                           | 0                                              | 0%       |  |

| Digital Verification IP: Design Quality Embodied Software: Design Quality | 0                                              | 0%       |  |

### **QIP Scoring**

- Score X weight for each rule

- Rule pass is counted, rule fail is uncounted

- Percentage of total is the final score

- Built-in QIP ruleset & policy

- Score & weight parameter for any rule

- Score & rating text in Summary

- Export report

- Considering bi-directional Excel feature

# **Top 5 Design Mistakes**

**Clock domain crossing**

Unsafe state machines

**Combinational feedback**

Unused or multiply-driven signals

**Incorrect sensitivity lists**

### **Incorrect Sensitivity Lists**

#### **Typical Causes:**

- **Edited code, but forgot sensitivity list**

- **Extra signals in the sensitivity list, just to be safe**

#### **Main Effects:**

- Can infer unintended latches

- Incorrect functional behavior

- RTL & Netlist simulation mismatches

- Extra signals slow simulation

# Unused or Multiply-Driven Signals

#### **Typical Causes:**

- Miss-spelling or connected wrong signal in an assignment

- Extra component port defined that is not needed

- Forgot to connect a port

#### **Main Effect:**

- **Unknown (X) values in simulation**

- Place & route errors

- **Unintended behavior**

#### **Combinational Feedback**

#### **Typical Causes:**

- No assignment inside a process sensitive to a clock

- Assignment is incorrect thus forming an unintended loop

#### **Main Effect:**

- Static timing analysis difficult or impossible

- Probably causes a functional bug

### **Unsafe State Machines**

#### **Typical Causes:**

- Incomplete specification

- No default case

- No recovery state

- Unreachable state

#### **Main Effect:**

Unrecoverable state

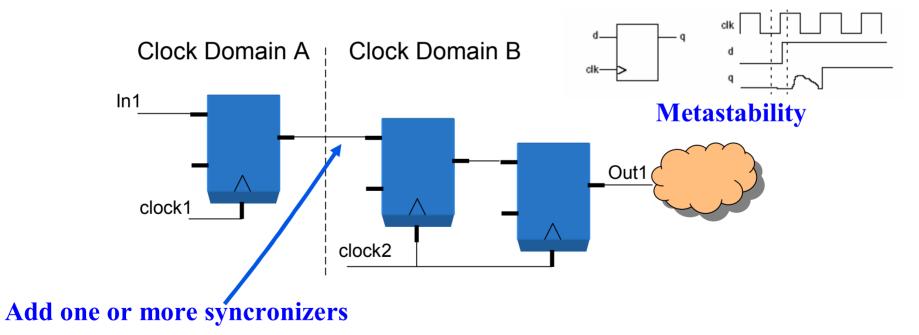

# **Clock Domain Crossing**

#### **Typical Issues:**

- Metastability neither a 1 or 0 is at the input & the wrong value is placed on the output

- Not typically detected by simulation

#### **Main Effect:**

Design creates incorrect logic at some point in time

### **Demo**

Design Import/Reference/SendTo

Hierarchy

Cross Reference, Where Used, Search, Unbound

Render Graphics – Documentation

VHDL Configurations – Generation Application

Version Management

Design Checking – As you write!

Properties/SideData

Flow customerisation – API, Simulation, Synthesis

Advanced Verification Techniques

# **Learning More**

HDL Designer & DesignAnalyst information is available at:

www.mentor.com/hdldesigner